Towards Terabit Carrier Ethernet and Energy Efficient Optical Transport Networks

Anders Rasmussen Ph. D. Thesis October 2013

# Towards Terabit Carrier Ethernet and Energy Efficient Optical Transport Networks

Ph. D. thesis Anders Rasmussen

DTU Fotonik,

Department of Photonics Engineering

Technical University of Denmark

October 2013

Supervisors Michael S. Berger Sarah Ruepp

#### Preface

This thesis represents the research carried out during my Ph. D studies from May 2010 to October 2013 at DTU Fotonik, Department of Photonics Engineering, Technical University of Denmark. The project has been supervised by Associate Professors Michael S. Berger and Sarah Ruepp and is partially funded by the Danish Advanced Technology Foundation (Højteknologifonden). The thesis is entitled "Towards Terabit Carrier Ethernet and Energy Efficient Optical Transport Networks" and investigates how future network elements can be scaled towards terabit-per-second capacities.

#### **Abstract**

This thesis focuses on the challenges of scaling current network node technology to support connection speeds of 100Gbps and beyond. Out of the many exiting aspects of reaching this goal, the main scope of this thesis is to investigate packet processing (address lookup and scheduling), forward error correction and energy efficiency.

Scheduling and address lookup are key functions and potential bottle necks in high speed network nodes, as the minimum packet/frame sizes in both the popular Ethernet protocol, as well as the Internet Protocol (IP) still remains constant (84B and 40B, respectively). Therefore, in order to support a single 100 Gigabit Ethernet link, the routing mechanism must be able to support address lookup and output scheduling of over 148 million packets per second (pps) leaving only a few nanoseconds for each packet. With the emerging standards for 400Gbps (400GE and OTU5) and discussions on how best to exceed the 1Tbps boundary, the packet processing rate requirements for future network nodes are likely to increase even further in the coming years. Hence, there lies a tremendous task in expanding and optimizing current technology and methodology to support these increasing requirements.

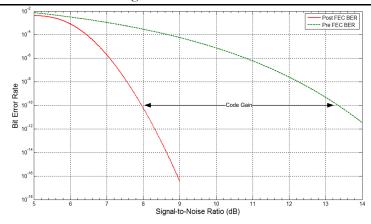

Forward Error Correction (FEC) is already a standard component of the Optical Transport Network (OTN) protocol as a means of increasing the bitrate-length product of optical links. However, the requirements for higher bitrates also drive a requirement for higher spectral efficiency in order to squeeze more traffic onto the existing physical transmission systems. To do this, while keeping the bit error rate (BER) below acceptable levels, more advanced FEC schemes are required. This is a challenge: Not only do we need to increase the processing speed of the FEC to handle the higher throughputs. The more advanced schemes also require more complex calculations to process each bit. This thesis will investigate how both the standard OTN FEC as well as more advanced FEC schemes can be implemented for 100G and above operation.

As the networks are expanded to run at increasingly higher speeds, an unfortunate by-product is higher energy consumption. While advances in the physical hardware production (e.g. better chip production techniques) somewhat reduces the problem, it is imperative to think energy efficiency into the systems from the early design stage to the actual implementation and operation. Similar to the now common practice within micro processors, recent research aims at dynamically balancing performance and energy consumption of optical communication systems based on the immediate capacity demands. This thesis will describe various ways of achieving this dynamic capacity/energy trade off, with special emphasis

on the Celtic project "Elastic Optical Networks" (EO-Net) and on adaptive forward error correction in particular.

#### Resumé

Denne afhandling omhandler udfordringerne i at skalere nuværende netværksnodeteknologi til at understøtte hastigheder på 100 gigabit per sekund og derover. Ud af de mange aspekter, som indgår i at nå dette mål, er fokus i denne afhandling lagt på pakkeprocessering (adresse opslag og schedulering), fremadrettet fejlkorrektion og energieffektivitet.

Schedulering og Adresse opslag er to nøglefunktioner og potentielle flaskehalse i højhastighedsnetværksnoder, da den mindste ramme/pakke størrelse i både den populære Ethernet protokol, samt i Internet Protokollen (IP), er holdt konstant (hhv. 84B og 40B). For at kunne understøtte 100 Gigabit Ethernet forbindelse. en rutningsmekanismerne derfor være i stand til at udføre adresseopslag og output schedulering af over 148 millioner pakker per sekund (pps), hvilket kun efterlader nogle få nanosekunder til at behandle hver pakke. Med de kommende standarder for 400Gbps (400GE og OTU5) og en igangværende diskussion om, hvordan man bedst overskrider 1 terabit/s grænsen, vil pakkeprocesseringshastigheden for fremtidige netværksknudepunkter med stor sandsynlighed stige endnu mere i de kommende år. Der ligger derfor en gevaldig opgave i at udvide og optimere nuværende teknologi og metoder til at understøtte disse stigende krav.

Fremadrettet fejlkorrektion (Forward Error Correction (FEC)) er allerede en standardkomponent i Optical Transport Network (OTN) protokollen, og tjener det formål at forøge bitrate-længde produktet på optiske forbindelser. Kravet om højere bitrater skaber også forøgede krav til spektraleffektiviteten for at klemme endnu mere kapacitet ud af eksisterende fysiske transmissionssystemer. For at gøre dette og stadig holde bitfejlsandsynligheden (BER) under et acceptabelt niveau, er det nødvendigt at benytte mere avancerede FEC metoder. Dette er en stor udfordring: Ud over at FEC systemerne skal køre hurtigere for at understøtte højere datarater, vil de mere komplicerede FEC metoder også kræve mere komplicerede udregninger for de enkelte bits. I denne afhandling vil det blive undersøgt, hvordan FEC systemet fra OTN, såvel som mere avancerede FEC metoder, kan implementeres til at køre med linierater på 100Gbps og derover.

En uheldig bivirkning ved de stadig større datahastigheder er øget energiforbrug. Til trods for at forbedringer af den fysiske hardwareproduktion til dels modvirker denne udvikling, er det yderst nødvendigt at tænke energieffektivitet ind i systemerne lige fra den tidlige designfase og indtil systemerne implementeres og tages i brug. I tråd med den nu gængse praksis indenfor mikroprocessorer, stiler nylig forskning efter dynamisk at afbalancere ydelse og energiforbrug i optiske kommunikationssystemer ud fra de øjeblikkelige kapacitetskrav. Denne

afhandling vil beskrive forskellige metoder til at opnå dynamisk afvejning mellem kapacitets- og energihensyn, med fokus på Celtic-projektet "Elatic Optical Networks" (EO-Net) og i særlig grad på adaptiv fremadrettet fejlkorrektion.

## Acknowledgements

The contents of this Ph. D. thesis would not have existed without the help, support and good company of a number of people.

Firstly, I would like to thank my supervisors Michael Berger and Sarah Ruepp for their invaluable guidance and support during the last few years. Whenever I needed help with an article, structural guidance for my Ph. D study, or just to brainstorm an idea, your doors were always open.

Secondly, I would like to thank the co-authors of my research papers for their important contributions to this thesis. Without your input, this work would be incomplete.

I would also like to thank Hao Yu, Ying Yan, José Soler, Anna Manolova, Henrik Wessing, Michael Berger and Sarah Ruepp for proof read and commenting on this thesis, and all of my colleagues at DTU Fotonik for making my stay at the institute a pleasant and inspiring one.

Finally, I would like to thank my family and friends for their support and encouragements, and especially my wonderful wife for her loving support throughout this journey.

Kgs. Lyngby, Denmark October 2013 Anders Rasmussen

#### **Publications**

#### **Published:**

- [P1] A. Rasmussen, J.Zhang, H. Yu, R. Fu, S. Ruepp, H. Wessing, M. Berger, "High Capacity Carrier Ethernet Transport Networks", WSEAS International conference: Recent Advances in Circuits, Systems, Signal and Telecommunications; Jan. 2010.

- [P2] A. Rasmussen, S. Ruepp, H. Wessing, M. Berger, J.V. Nielsen, H. Hurvig, "Framed Bit Error Rate Testing for 100G Ethernet Equipment", HPSR 2010 - 11th International Conference on High Performance Switching and Routing; June 2010.

- [P3] A. Rasmussen, J.Zhang, H. Yu, R. Fu, S. Ruepp, H. Wessing, M. Berger, "Towards 100G Carrier Ethernet Transport Networks", Journal: WSEAS Transactions on Communications, 2010.

- [P4] **A. Rasmussen**, S. Ruepp, M. Berger, H. Wessing, "High-speed Parallel Forward Error Correction for Optical Transport Networks", BONE-TIGER2 Summer School, 2010.

- [P5] S.Ruepp, H. Wessing, J. Zhang, A. V. Manolova, A. Rasmussen, L. Dittmann, M. Berger, "Evaluating Multicast Resilience in Carrier Ethernet", WSEAS International conference: Recent Advances in Circuits, Systems, Signal and Telecommunications; Jan. 2010.

- [P6] S.Ruepp, H. Wessing, J. Zhang, A. V. Manolova, A. Rasmussen, L. Dittmann, M. Berger, "Evaluating Multicast Resilience in Carrier Ethernet", Journal: WSEAS Transactions on Communications, Issue 2, Vol. 9, 2010.

- [P7] H. Wessing, M. S. Berger, H. M. Gestsson, H. Yu, A. Rasmussen, L. J. Brewka, S. R. Ruepp, "Evaluation of restoration mechanisms for future services using Carrier Ethernet", in journal: W S E A S Transactions on Communications, vol: 9, issue: 5, pages: 322-331, 2010.

- [P8] H. Wessing, M. S. Berger, H. Yu, A. Rasmussen, L. J. Brewka, S. R. Ruepp, "Evaluation of Network Failure induced IPTV degradation in Metro Networks", 4th WSEAS International Conference on Circuits, Systems, Signal and Tele-communications, Cambridge, 2010.

- [P9] S. R. Ruepp, H. Wessing, J. Zhang, A. M. Fagertun, A. Rasmussen, L. Dittmann, M. S. Berger, "Providing resilience for carrier ethernet multicast traffic", 4th WSEAS International Conference on Circuits, Systems, Signal and Telecommunications, Cambridge, 2010.

- [P10] Ruepp, S., Rytlig, A., Berger, M., Wessing, H., Manolova, A. V., Yu, H., & Rasmussen, A., "Evaluation of Speedup and Expansion in Terabit Switch Fabrics", In Proceedings of OPNETWORK 2011.

- [P11] **A. Rasmussen**, S. Ruepp, M. Berger, H. Wessing, H. Yu, "SDRAM-based packet buffer model for high speed switches", OPNETWORK 2011 Conference Proceedings, 2011.

- [P12] S. Ruepp, A. Rytlig, M. S. Berger, H. Wessing, A. V. Manolova, H. Yu, A. Rasmussen, "Evaluation of Speedup and Expansion in Terabit Switch Fabrics", OPNETWORK 2011 Conference Proceedings, 2011.

- [P13] H. Hu, J. D. Andersen, A. Rasmussen, B. M. Sørensen, K. Dalgaard, M. Galili, M. Pu, K. Yvind, K. J. Larsen, S. Forchhammer, L. K. Oxenløwe, "Forward error correction supported 150 Gbit/s error-free wavelength conversion based on cross phase modulation in silicon", Optics Express vol: 21, issue: 3, 2013.

- [P14] H. Hu, D. Kong, E. Palushani, J. D. Andersen, A. Rasmussen, B. M. Sørensen, M. Galili, H. C. H. Mulvad, K. J. Larsen, S. Forchhammer, P. Jeppesen, L. K. Oxenløwe, "1.28 Thaud Nyquist Signal Trans-mission using Time-Domain Optical Fourier Trans-formation based Receiver", Conference on Lasers and Electro-Optics (CLEO 2013), San Jose, California, 2013.

- [P15] A. Rasmussen, A. Kragelund, M. Berger, H. Wessing, S. Ruepp, "TCAM-based High Speed Longest Prefix Matching with Fast Incremental Table Updates", Winner of "Best Student Paper Award", HPSR 2013.

- [P16] A. Rasmussen, S. Ruepp, M. S. Berger, K. J. Larsen, "Adaptive Forward Error Correction for Energy Efficient Optical Transport Networks", HPSR 2013.

#### Accepted to be published:

- [P17] A. Rasmussen, H. Yu, S. Ruepp, M. S. Berger, L. Dittmann, "Efficient Round-Robin Multicast Scheduling for Input-Queued Switches", IET Networks, 2013.

- [P18] Anders Rasmussen, Metodi P. Yankov, Michael S. Berger, Knud J. Larsen, Sarah Ruepp," Improved Energy Efficiency for Optical Transport Networks by Elastic Forward Error Correction", Journal of Optical Communications and Networking (JOCN).

### Table of Contents

| 1. | INTRODUCTION                                                    | 1  |

|----|-----------------------------------------------------------------|----|

|    | 1.1. Thesis organisation                                        | 4  |

| 2. | 100 GIGABIT ETHERNET AND BEYOND                                 | 7  |

|    | 2.1. THE CHALLENGE OF 100GE AND BEYOND                          | 7  |

|    | 2.1.1. Basic line card structure                                |    |

|    | 2.1.2. Datapath architecture                                    |    |

|    | 2.1.3. Address lookup                                           | 9  |

|    | 2.1.4. Memory                                                   |    |

|    | 2.1.5. Traffic management                                       |    |

|    | 2.1.7. Improvements in FPGA technology                          | 14 |

|    | 2.1.8. Conclusions on the challenges of 100 GE and beyond       | 15 |

|    | 2.2. ETHERNET AS A CARRIER TECHNOLOGY                           |    |

|    | 2.3. STANDARDIZATION OF 100 GIGABIT ETHERNET                    | 19 |

|    | 2.3.1. 100G Media Independent Interface                         | 19 |

|    | 2.3.2. 100G Attachment Unit Interface                           |    |

|    | 2.4. FRAMED BIT ERROR RATE TESTING FOR 100GE                    |    |

|    | 2.4.1. Clock Frequency Versus Buswidth                          |    |

|    | 2.4.2. Bit Error Rate Testing                                   |    |

|    | 2.4.3. Framed BERT2.4.4. Synthesis Results                      |    |

|    | 2.4.5. Conclusion on Framed BERT                                |    |

|    | 2.5. CHAPTER SUMMARY                                            |    |

| 2  | ADDRESS LOOKUP                                                  |    |

| Э. | 3.1. MAC TABLE LOOKUP                                           |    |

|    | 3.1.1. Background                                               |    |

|    | 3.1.2. Related work on hash tables                              |    |

|    | 3.1.1. Chained hash tables                                      |    |

|    | 3.1.2. Hash Distribution and Performance of Chained Hash Tables |    |

|    | 3.1.3. Multilevel Adaptive Hash Tables                          |    |

|    | 3.1.4. Hash table for 100GE                                     |    |

|    | 3.1.5. Conclusions on MAC table lookup                          |    |

|    | 3.2. IP LOOKUP                                                  |    |

|    | 3.2.1. Common RAM-based data structures for IP lookup           |    |

|    | 3.3. TCAM-BASED HIGH SPEED LONGEST PREFIX MATCHING              |    |

|    | 3.3.1. Background                                               |    |

|    | 3.3.3. LPM With Modified TCAM                                   |    |

|    | 3.3.4. Resource Utilization and Performance Analysis            |    |

|    |                                                                 |    |

| 3.3.5. Conclusions on TCAM-based LPM                                                              | 57  |

|---------------------------------------------------------------------------------------------------|-----|

| 3.4. Chapter Summary                                                                              |     |

| 4. MULTICAST SWITCH FABRIC SCHEDULING                                                             | 59  |

| 4.1. INTRODUCTION TO SWITCH FABRIC SCHEDULING                                                     |     |

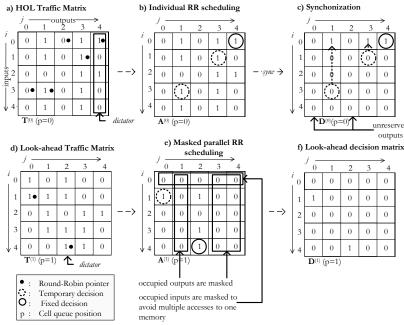

| 4.2. EFFICIENT ROUND ROBIN MULTICAST SCHEDULING                                                   |     |

| 4.2.1. Related Work                                                                               |     |

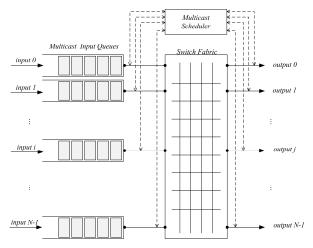

| 4.2.2. System Model                                                                               | 63  |

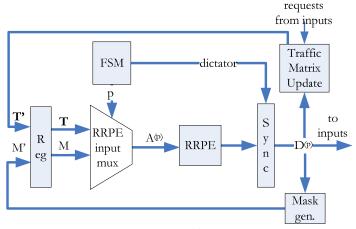

| 4.2.3. Efficient Round-Robin Multicast Scheduling Algorithm.                                      |     |

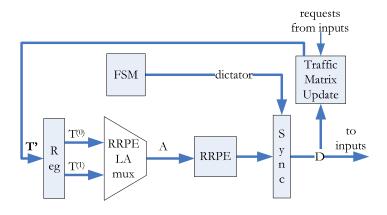

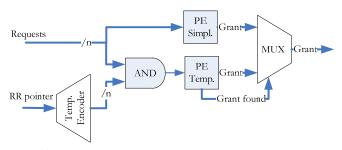

| 4.2.4. Hardware Implementation                                                                    |     |

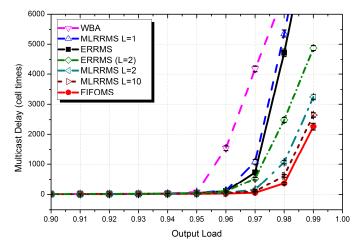

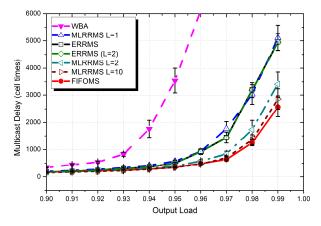

| 4.2.5. Simulation Results                                                                         |     |

| 4.3. CHAPTER SUMMARY AND ERRMS CONCLUSION                                                         |     |

|                                                                                                   | / / |

| 5. HIGH PERFORMANCE FORWARD ERROR CORRECTION                                                      | 79  |

| 5.1. Background                                                                                   |     |

| 5.1.1. Low Density Parity Check Codes                                                             |     |

| 5.1.2. Concatenated FEC Codes                                                                     |     |

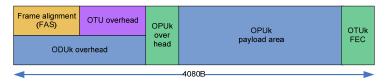

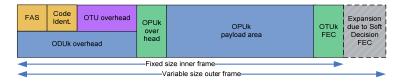

| 5.2. REED SOLOMON FEC FOR OTN4                                                                    |     |

| 5.2.1. RS FEC operation in OTN                                                                    | 84  |

| 5.2.2. Parallel RS FEC implementation                                                             |     |

| 5.2.3. Synthesis Results5.2.4. Reed Solomon Summary                                               | 86  |

|                                                                                                   |     |

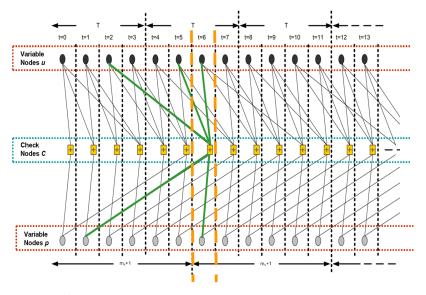

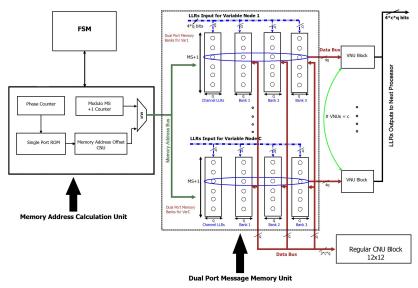

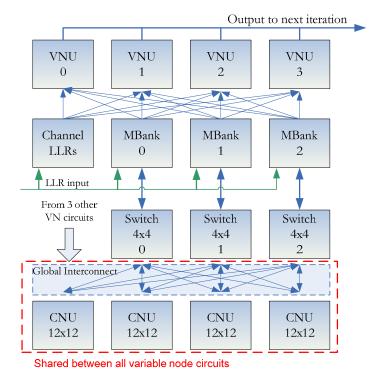

| 5.3. PARALLEL LDPC-CC FOR HIGH SPEED CONNECTIO 5.3.1. Encoder                                     |     |

| 5.3.2. Decoder                                                                                    |     |

| 5.3.3. Synthesis Results                                                                          |     |

| 5.4. CHAPTER SUMMARY                                                                              |     |

| 6. ENERGY EFFICIENT OPTICAL TRANSPORT                                                             |     |

| NETWORKS                                                                                          | 95  |

| 6.1. OVERVIEW OF ELASTIC OPTICAL NETWORKS                                                         | 95  |

| 6.2. ADAPTIVE FORWARD ERROR CORRECTION                                                            |     |

| 6.2.1. Related Work                                                                               |     |

| 6.2.2. Rate Adaptive Channel Coding                                                               |     |

| 6.2.3. Frame-by-Frame Rate Adaptation6.2.4. Power Reduction Through Adaptive Iteration Reduction. |     |

| 6.2.5. Simulation Results                                                                         |     |

| 6.3. Chapter Summary                                                                              |     |

| 7. CONCLUSION                                                                                     |     |

| 8. REFERENCES                                                                                     |     |

| V. ILI LILI IOLU                                                                                  | 11/ |

#### 1. Introduction

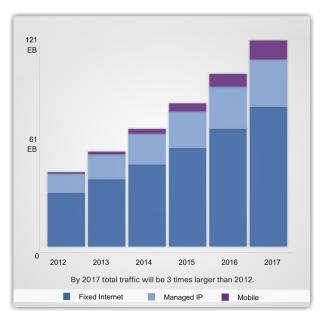

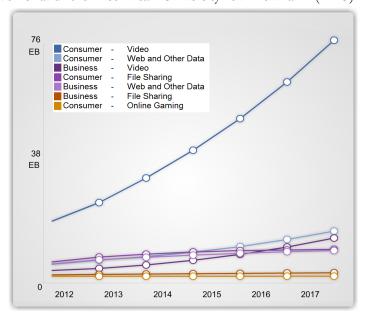

Global Internet traffic is rising at a remarkable pace. The increasing popularity of bandwidth intensive services such as Internet-based video streaming (Netflix, YouTube, IPTV), video telephony (Skype, FaceTime), and cloud services has provided a demand for very high speed internet connections as well as the applications to utilize bandwidth over long periods of time. Combined with the expanding high speed mobile and land based access networks, this has given rise to an unprecedented increase in internet traffic over the past few years - a trend which is likely to continue for years to come. According to the Cisco Visual Networking Index (CVNI), global internet traffic has increased more than fourfold in the past five years and is expected to increase threefold over the next five years (see Figure 1.1)[1]. When it comes to which kinds of services will dominate the growth in internet traffic, the prediction from CVNI (Figure 1.2), is crystal clear: Video, video, and more video. The slow dialup modems and grainy internet videos are truly a thing of the past. And, where internet based video-on-demand used to be synonymous with internet piracy, there are now plenty of legal content providers, supplying users with high quality content immediately and directly to their high definition televisions or mobile displays.

Figure 1.1 – Projected growth in monthly internet traffic 2012-2017 [1].

With this rise in traffic in the access part of the network, there is an increasing demand for high speed connections in the transport networks to handle the aggregated traffic. Instead of simply installing more links using the existing 10G standards (e.g. OTN2 and 10G Ethernet), new standards for 40G and 100G have paved the way for a 4-10 fold increase in the capacities of each logical link. When work presented in this thesis started in May 2009, the 40G and 100G standards were not yet finalized and equipment was still under development [2]. Now, 40G and 100G equipment is commercially available and current standardization and research efforts are focused on extending the 40G/100G architectures to 400G and eventually beyond the 1T boundary [3]–[7].

Increasing the link capacities above 100Gbps impacts the communication systems at multiple levels. The primary focus of this thesis is the challenges which arise at the network node level, when moving to 100G and beyond. Every sub-system, from the switch interconnection fabric and the buffering systems to the packet processors, needs to be redesigned and/or upgraded to support these high speeds. The Danish research project "The Road to 100 Gigabit Ethernet", which ended successfully in May 2012, aimed specifically at meeting these challenges. The aim of the project was to (a) design and implement a 100GE line card with a packet processor and a traffic manager, (b) design and implement a 100GE tester capable of generating and verifying Ethernet framed data at 100Gbps and (c) model and simulate new system architectures and algorithms for 100 Gigabit operation. The three partners in the project, TPACK, Xena Networks and the Technical University of Denmark (DTU) were

Figure 1.2 – Projected service distribution 2012-2017 (EB/month) [1].

responsible for (a), (b) and (c), respectively. Out of the work done in this project, this thesis focuses specifically on the research within packet processing, in terms of address lookup and packet scheduling, and the development of a 100GE framed bit-error-rate tester (BERT).

At the physical layer, the classical Wave Division Multiplexing (WDM) channel slot size of 50GHz can just barely support 100Gbps with the current modulation formats [8]. Hence in order to reach above this speed, it is either necessary to split up the 400G signal into several serial streams (just like the 100GE standard specifies[9]) or to use larger channels. An alternative is to use more spectrum efficient modulation formats, which in term requires higher signal-to-noise ratios (SNR) and more signal processing to achieve the same bit-error-rate (BER) of the transmitted information. While all aspects of the physical transmission are important, this thesis will limit itself to the forward error correcting codes used at the physical layer to aid in increasing spectral efficiency.

A final aspect of high speed networking, which is important across the layers, is energy efficiency. Energy efficiency is both important from an economical and environmental point of view, but also for pure technical reasons, as high power consumption requires larger power supplies and more effective cooling of the systems. Part of the work leading up to this thesis was done as part of the European CELTIC project "Elastic Optical Networks (EO-Net)" [10]. This project focussed specifically on introducing dynamic power reduction into the transport networks as a mean of trading off throughput for lower power consumption in off-peak periods. Partners in the project included members of academia (DTU, Chalmers University of Technology, Nordunet), equipment / IP-core providers (Alcatel-Lucent Bell Labs, Ekinops, Analogies, C2Tech) and a service provider (France Telecom / Orange labs). Aside from giving a general overview of this work, the thesis describes in detail some of the efforts put into designing and implementing dynamic forward error correction (FEC) for high performance FEC codes.

#### 1.1. Thesis organisation

This section provides an overview of the thesis structure and the content of the individual chapters. Some sections presented here have been written specifically for this thesis, while others are based on published research articles, which have been updated and expanded for the thesis. Of the 16 published and 2 pending journal and conference publications, which were co-authored as part of this Ph. D. study, only the papers most relevant to the research area has been chosen for inclusion in this thesis. The list of papers and their respective sections is shown in Table 1.1.

Chapter 2 gives a general introduction to the challenges of pushing Ethernet towards 100Gbps and beyond, while elevating Ethernet to function as a transport protocol. The chapter also contains a section (2.4) on bit error rate testing on 100G Ethernet connections, attaching the bit error rate tester (BERT) directly to the 100G Media Independent Interface (CGMII). As a prelude to Section 2.4, Section 2.3 provides a brief description of the CGMII and CAUI interfaces and how they differ from the previous 10G standard (XGMII and XAUI). Sections 2.3 and 2.4 are based on papers [P3] and [P2], respectively.

Chapter 3 looks into the issue of performing address lookups at this high speed, specifically on MAC table lookups (Ethernet), and on IP table lookups (Internet Protocol) with special emphasis on a novel TCAM-based scheme for Longest Prefix Matching (LPM). The TCAM section (3.3) is based on paper [P15].

Chapter 4 deals with multicast scheduling and investigates how this can be performed efficiently in high speed, high port count network nodes. This chapter is based on paper [P17].

| Section | Papers | Author Number   |

|---------|--------|-----------------|

| 2.3     | [P3]   | 1st             |

| 2.4     | [P2]   | 1 <sup>st</sup> |

| 3.3     | [P15]  | 1 <sup>st</sup> |

| 4       | [P17]  | 1st             |

| 5.1     | [P18]  | 1st             |

| 5.2     | [P4]   | 1st             |

| 6       | [P18]  | 1st             |

Table 1.1 - Sections of the thesis based on research papers.

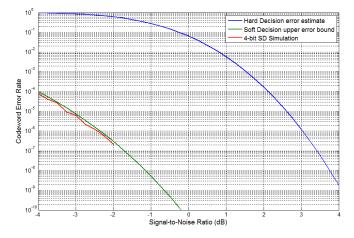

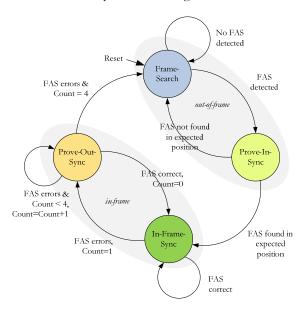

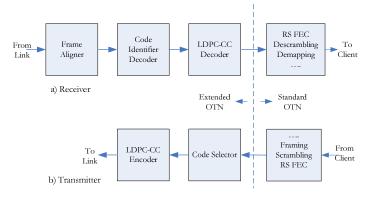

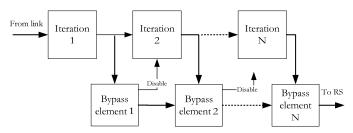

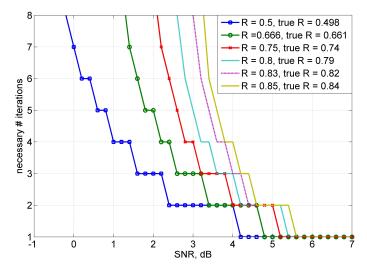

Chapter 5 investigates the issue of performing forward error correction (FEC) at high speed. Firstly, the section provides a short introduction to FEC codes, with specific emphasis on the codes used in this project, and introduces the concept of concatenated codes [P18]. Secondly, a case study is described, of a 100Gbps implementation of the Reed-Solomon (255,239) FEC, commonly used in the Optical Transport Network (OTN) protocol, using a Field Programmable Gate Array (FPGA) (based on paper [P4]). Lastly, it is shown how the more complex soft decision Low Density Parity Check (LDPC) FEC can be scaled towards 100Gbps as well.

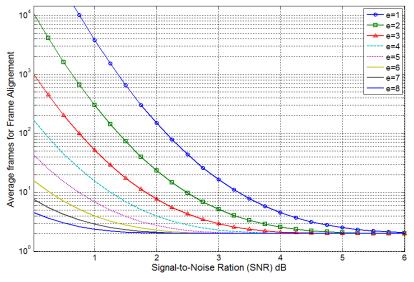

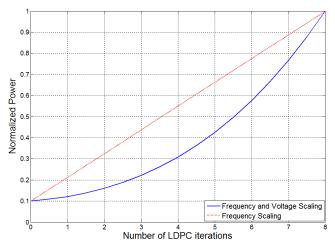

Chapter 6 examines high speed networks from a power-efficiency point of view with specific emphasis on reducing the power consumption of the FEC circuits (based on paper [P18]).

Chapter 7 concludes the thesis.

## 2. 100 Gigabit Ethernet and Beyond

In the beginning of the project "The Road to 100 Gigabit Ethernet" (100GE) in 2009, 10 Gigabit links were widely deployed in the transport networks [11]. This is still the case. However, as the internet users' behavioral patterns have moved towards more bandwidth intensive applications, along with the increasing use of cloud services, the demand for extra capacity in the transport networks and data centers have increased correspondingly. The new 100G standards, for OTN (OTU-4) and 100 Gigabit Ethernet (100GE) [9], are capable of fulfilling these bandwidth demands, handling millions of packets per second, and efforts are already being made to develop a new 400G standard[6]. In 2009, when the 100G project started, the underlying hardware technology was just evolved to the point where 100G systems were viable, and even with the recent improvements in chip-technology, memory technology etc., building efficient 100G systems (not to mention 400G systems!) is still no trivial task. The purpose of this chapter is to provide a general overview of the 100GE standard as well as the challenges of designing network equipment, which can operate at 100G and beyond, taking into account recent advances in chip and memory technology.

#### 2.1. The challenge of 100GE and beyond

The main area of research in the 100G project has been the challenges of scaling Ethernet capacity from the 2009 state-of-the-art at 10Gb/s to next generation 100Gb/s. The challenges includes interface adaptation, data and control plane processing, switching, power and printed circuit board requirements. The original goal of 100Gb/s was very ambitious, and required first of all improvements in the low level circuit technology. However, these improvements were far from enough to deliver a factor 10 in performance when moving from 10Gb/s to 100Gb/s, and even less so when looking to future 400G connections.

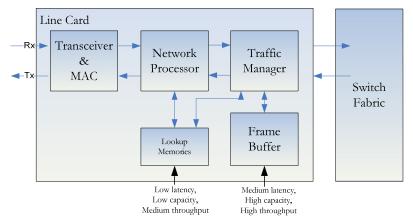

#### 2.1.1. Basic line card structure

The basic structure of a 100GE line card is depicted in Figure 2.1. The first logical block in on the line card is the transceiver and the Medium Access Control (MAC) block. Since all 100G modules work in full duplex and no auto negotiation is supported, the functionality of the Medium Access Control (MAC) is reduced to Frame Check Sum (FCS) generation and validation (in the TX and RX direction, respectively). The basic functions of the transceivers are described in greater detail in Section 2.3. Once the data has been received and validated, it enters the network processor (NP), which performs classification tasks, such as MAC address and VLAN lookup to determine the forwarding port(s), and Class of Service (CoS) determination. The NP is also responsible for automatic MAC address learning. These functions require lookup tables, which can be accessed very frequently, but which generally do not need to be very large in terms of memory consumption. The issue of address lookup is elaborated further in sub-section 2.1.3. Once classified, the frames move on to the traffic manager (TM). The task of the TM is to determine the QoS of the packets, based on metering and the information provided by the NP, and to shape and prioritize the traffic flows based on this information, as well as other information, such as flow control messages from its peers. Hence, the TM is responsible for the overall scheduling of frame departures into the switch fabric. As such, the TM is also responsible for frame buffering. For the purpose of frame buffering, high throughput and high capacity memory is needed. While access latency is also an issue for the frame buffers, the requirements are not quite as stringent as for the lookup memories. The TM is described in further detail in sub-section 2.1.5. Finally, the frames are relayed to the switch fabric, which interconnects all the line cards in the switch (further details in subsection 2.1.6).

Figure 2.1 – Basic linecard architecture.

#### 2.1.2. Datapath architecture

Since, the basic structure of the Ethernet frames at the MAC level has not changed with the new 100GE standard, an attractive solution would be to simply run the existing 10G designs at 10 times the clock frequency. Unfortunately, despite continuous advances in FPGA performance, increasing the clock frequency is not in itself a viable solution to the problem. Another approach could be to balance the incoming traffic between multiple 10G designs. This allows for reuse of existing logic blocks, running closer to their designed max clock frequency. The tradeoff here is increased chip area, higher latency (since each packet is processed slower than 100Gbps), managing resource sharing amongst multiple packet processors (forwarding tables etc.) and a significant challenge in balancing the traffic while avoiding frame reordering. A final approach would be to redesign the system to work with a wider data path i.e. to process more bits in parallel at a lower clock frequency. This poses some challenges to the designer. The authors of the 100GE standard have been kind enough to impose a 8 byte alignment of the Start-of-Frame (SOF) at the CGMII interface[9], which eases the initial frame alignment, even for wide data busses. Unfortunately, the length of the frames can still be any integer number of bytes, which makes e.g. parallel CRC calculation more difficult and poses the potential problem of poor internal bandwidth utilization for packets sizes which are not an integer division of the bus width.

#### 2.1.3. Address lookup

A crucial part of an Ethernet switch is its ability to build and maintain its forwarding table and to perform fast lookups in the table to make forwarding decisions for the individual packets at line speed. To keep up with the worst case traffic patterns of just a single 100GE link, this table must be able to handle up to 298 million lookups per second to handle the combined destination address lookups and source information updates. Furthermore, since switches rarely consist of just a single port, the table structure needs to scale to handle traffic from multiple ports. Popular technology choices for MAC address tables include linked lists, hash tables and Content Addressable Memories (CAMs), depending on the requirements of the system. Due to the importance of address lookup mechanisms, this subject has been given its own chapter in this thesis. Section 3.1 and Sections 3.2-3.3 discuss the issues of address lookups in Ethernet switches and IP routers respectively.

#### **2.1.4.** Memory

In a perfect world, all data structures would be kept in high speed on-chip memory. Unfortunately, the large data structures required to perform traffic management, ensure QoS (Quality of Service), perform packet buffering, etc. are too much to keep in on-chip memory alone. Hence, access to high speed external memory is a necessity. This is a substantial challenge when going from 10G to 100G, because the speed of memory does not follow Moore's famous law, stating that the processing power will double around every second year. Especially the larger DRAM-based memories have performance issues when data is stored or accessed in a non-sequential manner (random access), even though there have been significant improvements with respect to the access bandwidth over the years, as seen in Table 2.1. Hence, a combination of different memory types, traffic shaping, and some degree of over-dimensioning of the memory bandwidth is necessary to reach 100Gbps [P11][12]-[15]. When moving on to higher speeds and/or denser systems, this becomes an even greater problem.

For the packet buffers, which require high density memory, i.e. DRAM, current technology is neither fast enough nor compact enough to reach the next goal of 400 Gigabit Ethernet. In order to implement a 400G packet buffer, the effective read/write bandwidth must be at least 800Gbps, assuming perfect bandwidth utilization. Even with state-of-the-art DDR4-2667 memory, this requires five DIMMs, each with 288 I/O pins (see Table 2.1). Hence, a total of 1.440 connections must be routed across the printed circuit board (PCB). The bandwidth bottle neck caused

| Technology             | BW<br>(Gbps) | Power (W) | mW/GB/s | pj/bit |

|------------------------|--------------|-----------|---------|--------|

| SDRAM<br>PC133*        | 8.48         | 4.96      | 4664.97 | 762    |

| DDR-333*               | 21.28        | 5.48      | 2057.06 | 245    |

| DDRII-667*             | 42.72        | 5.18      | 971.51  | 139    |

| DDR3-1333*             | 85.28        | 5.52      | 517.63  | 52     |

| DDR4-2667*             | 170.72       | 6.60      | 309.34  | 39     |

| GDDR5*                 | 160          | 2.70      | 135.00  | 16.88  |

| LPDDR2-<br>1066 Die    | 34.08        | 0.43      | 100.2/8 | 12.54  |

| HMC Gen1<br>512MB Cube | 1024         | 11.08     | 86.53   | 10.85  |

Table 2.1 Comparison of memory technologies[20][120].

by access dependent internal delays inside the DRAM [P11], can to some extent be minimized by clever memory management [13]. Even so, the actual bandwidth requirements are likely to be significantly higher than 800Gbps.

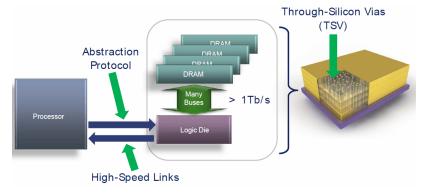

In recent years, the trend within external memory is moving towards memory architectures with high-speed serial interfaces, as opposed to the classical approach of using wide parallel busses[16]-[18]. Using serial interfaces drastically lowers chip I/O overhead and makes it viable to use off-chip packet buffers with enough inter-chip bandwidth to sustain 400G throughput. One such technology is the so called Hybrid Memory Cube (HMC) [19], [20], which has been created by a consortium of developers (Micron, IBM, Altera, Xilinx etc.) and adapters (Napatech, Synopsys, AIRBUS etc.). The HMC is basically a 3D structure as depicted in Figure 2.2, consisting of one logic layer (the controller) and 4-8 layers of DRAM, all interconnected with high speed through-silicon-vias (TSVs). The interface to the memory is through multiple 10G-15G serial links (full duplex). According to the consortium, the resulting memory bandwidth is more than 15x higher than DDR3, using 70% less energy and taking up 90% less space, compared to the common DIMM solution[16]. This is in part a result of the new stacked architecture, the built in controller and a high degree of subdivision of the memory (128-256 banks as opposed to 8 banks in a standard DIMM).

If the promises of the HMC technology hold true, it will go a long way towards satisfying the memory bandwidth requirements and random access performance necessary to make the next jump to 400G. A 2011 demo of the HMC by Micron showed a sustained throughput of just under 1Tbps using 50nm DRAMs and 90nm technology for the logic controller[20]. The newly release specification allows for 32 to 64 links (10G-15G) or up to 128 links (10G). Thus, the maximum aggregated bandwidth supported by this specification (incl. overhead) is 2.56Tbps[19]. Using this technology, the corresponding I/O count for

Figure 2.2 – Hybrid Memory Cube (HMC) arcitecture. (HMC height is exaggerated)[20].

supporting 800Gbps of effective read/write bandwidth is 200 pins, assuming 10G differential transceivers and 64B read/writes. The first version of the HMC specification was recently published[19], and according to Micron, the first commercial HMCs will be ready by the end of 2013. Early samples of Altera's first FPGA to support HMC, the Arria 10, will be ready in the beginning of 2014, supporting 1.28Tbps aggregated HMC bandwidth.

As described in subsection 2.1.1, data structures related to MAC address lookup, flow identification, policing, statistics counters and similar functions in the network processor (NP) and traffic manager (TM), do not require a high density memory, but rater memory with excellent random access performance. For this purpose, SRAM based memory is a good choice due to its low and address-independent access latency. One of the fastest SRAM memory types on the market is Quad Data Rate (QDR)-II+ SRAM. QDR uses separate read and write data busses, each of which employs Double Data Rate (DDR) transmission. This eliminates the bus turn-around delay found in shared bus memory types (like DDR SRAM). Currently, QDR memory comes in 9-bit, 18-bit and 36-bit bus width configurations with up to 144Mb of memory. State-of-the-art QDR-II+ XTreme (72Mb) runs at up to 633MHz, corresponding to 316.5 million transfers per second (MT/s) of four words bursts in both the read and the write direction simultaneously [21]. For lower speed applications, Reduced Latency DRAM (RLDRAM) is a viable alternative, providing higher memory density than SRAM with a significantly better random access performance than standard DDR3 RAM.

#### 2.1.5. Traffic management

The task of the traffic manager is to manage the bandwidth of the packet flows based on multiple criteria such as latency, packet loss, bandwidth guarantees, latency and jitter to meet the Quality of Service (QoS) guarantees given to the users. This management includes metering and policing of individual flows, as well as performing traffic shaping, queuing and scheduling are based on this information. The challenge when moving to 100G and beyond is mainly that the processing capacity of the switches in terms of frames per second, as well as the potential number of flows, increases significantly. This poses significant challenges throughout the traffic manager. First of all, the data structures for metering, policing etc., needs to be updated at up to 10 times the frequency of a 10G system. With the high number of flows, these data structures cannot comfortably fit in on-chip memory, and must be stored in high speed external memory such as the QDR-II+ SRAM mentioned in Section 2.1.4. With current state-ofthe-art QDR-II+ SRAM, it is possible to perform up to 316.5M read- and write operations per second on 36 to 144 bits (device specific). This allows for more than two 144-bit statistics updates for each frame on a 100G

link, assuming minimum sized packets[21]. Given the small I/O count and high performance of QDR memory, this technology is well suited for 100G line cards and appears to be scalable to higher line rates as well.

Another challenge lies in the packet scheduling function. The purpose of the scheduler is to assure that the packets are relayed to the switch fabric in a fair manner, taking the mentioned flow priorities into account. This involves ordering the packets into multiple queues based on metrics such as output port and priority, and arranging the packet departures from the queues by means of a weighted scheduling scheme, e.g. Deficit Weighted Round-Robin or Weighted Fair Queuing [22], [23].

#### 2.1.6. Switch Fabric

Fast processing and efficient queuing is of little help if the underlying switch fabric is not able to keep up with the aggregated line speed. For switches with a relatively low number of ports, the buffered cross-bar architecture yields high switching performance and no blocking. Unfortunately, the number of cross-points as well as the required amount of buffer memory grows proportionally with the square of the number of ports  $(O(N^2))$ , making this architecture impractical for large switch fabrics[24]–[26]. A more scalable approach is employing self-routing switch fabric architectures, such as Clos or Banyan networks. The basic concept of these architectures is to build up the switch fabric as a network of smaller (e.g. two- to four-port) switches. The advantage of this structure is that the total number of cross-points is lower than that of a corresponding full scale cross-bar. The trade-off is some added routing complexity, and in the case of Banyan networks, a small probability of internal blocking[24]. As part of the 100GE project, the Clos-design has been investigated through modeling and simulation[27][P10]. This research revealed only minor performance penalties compared to the crossbar architecture with the benefit of higher scalability. From these results, it seems that self-routing switch fabrics are indeed a viable solution to realize next generation high speed, high port count switches.

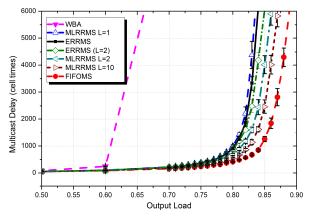

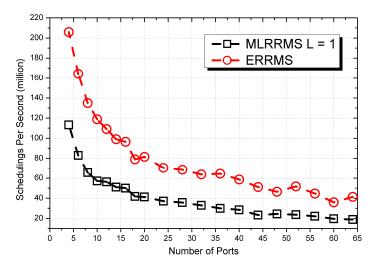

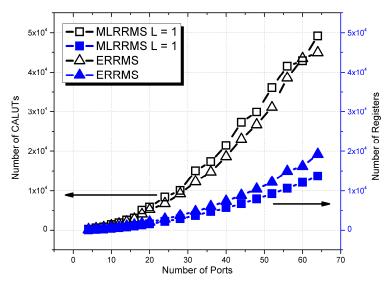

Like for the traffic manager, mentioned in 2.1.5, high performance switch fabrics will themselves contain a queuing system and an accompanying scheduler. As opposed to the priority-based TM schedulers, the fabric scheduler has one simple purpose: to assure optimal utilization of the output ports and minimal packet latency under the constraints of the underlying switch fabric and queuing system. While it is always possible to find the optimal scheduling solution given enough time and resources, it is rarely the optimal choice from a practical implementation point of view – especially as the number of output ports increases. Usually, it is more prudent to go for an algorithm, which converges faster (optimally within a fixed runtime) at the cost of lower worst case output utilization and/or higher internal bandwidth requirements. In the case of large scale switches,

it is also important to take into account how the calculation complexity scales with the number of ports and how much the scheduling can be segmented to take advantage of hardware parallelism. Section 4 looks further into the switch fabric scheduling problem with special emphasis on efficient scheduling of multicast packets.

#### 2.1.7. Improvements in FPGA technology

Clever design goes a long way towards improving the performance of network devices. However, the 2009 chip technology used to reach 100 gigabit operation cannot support the next step moving towards 400 gigabit connections. Luckily, the chip manufactures have made significant progress in terms of improving the speed, density and power efficiency of their products. In 2009, when the 100GE project started, the then most advanced FPGAs from Altera were selected for implementing the 100G line card and the accompanying tester. The FPGA type used for these two systems was from the Stratix IV family. This FPGA was based on 40nm technology, featuring 530k logic elements (LE) and 24 transceivers running up to 11.3Gbps.

As seen in Table 2.2, there has been a significant development during the last four years. The basic production technology has moved from 40nm to 28nm, with 20nm devices announced for 2014 and a 14nm Stratix 10 device in the pipeline. This has made it possible to produce FPGAs, which are both faster and denser. Hence, the number of available logic blocks and on-chip memory has increased by around a factor of two compared

| Year           | Device<br>Family | Tech. | LEs*  | Transceivers | Memory<br>(Mbits) |  |

|----------------|------------------|-------|-------|--------------|-------------------|--|

| Altera Devices |                  |       |       |              |                   |  |

| 2009           | Stratix IV GT    | 40nm  | 530k  | 24@11.3Gbps  | 20.3              |  |

| 2011           | Stratix V GT     | 28nm  | 952k  | 4@28Gbps     | 52                |  |

|                |                  |       |       | 32@12.5Gbps  |                   |  |

| 2014           | Aria 10 GT       | 20nm  | 1150k | 96@28Gbps    | 53                |  |

| Xilinx Devices |                  |       |       |              |                   |  |

| 2009           | Virtex-6         | 40nm  | 504k  | 48@6.6Gbps   | 32.8              |  |

|                |                  |       |       | 24@11.3Gbps  |                   |  |

| 2012           | Virtex-7         | 28nm  | 778k  | 16@28Gbps    | 68                |  |

|                |                  |       |       | 72@13.1Gbps  |                   |  |

Table 2.2 - Evolution of FPGA technology[30], [40]

<sup>\*</sup>Xilinx "Logic Cells" converted to the Altera "Logic Elements" based on a 1.125:1 ratio [40].

to the 2009 generations. Likewise, the aggregated transceiver bandwidth has increased by almost a factor of ten in the coming Aria 10 GT device compared to the Stratix IV GT from 2009. With this amount of high speed transceivers, it is possible to run 400Gbps bi-directional traffic through the device (2x16x25Gbps), while supporting 960Gbps of full duplex bandwidth (incl. overhead) to an external HMC memory device (4x16x15Gbps). Hence, from a transceiver bandwidth perspective, the next generation FPGA technology should be able to support 400G operation with external memory queues. A more difficult question is whether the increased speed and logic density will be enough to process information at this speed. According to Altera, they expect the core performance of the next generation chips to scale approximately linearly with the transistor size. This indicates a factor two increase in processing power for the Aria 10 compared to the Stratix IV GT. Along with the factor two increase in the number of logic elements, it will likely be possible to reach 400Gbps processing throughput by careful optimization and parallelization. While initial designs are likely to be FPGA based until the standards are finalized and a suitable architecture has been found, mass production of 400G devices will most likely be done using Application Specific Integrated Circuits (ASICs)[28]. This will drive down the per-unit cost (given enough volume) and allow for a much higher degree of integration with significantly lower power consumption compared to FPGA-based systems.

## 2.1.8. Conclusions on the challenges of 100 GE and beyond

This subsection has highlighted some of the challenges in reaching 100 gigabit line speed and pushing it further towards the future 400G standards. It is clear that there has been significant improvements in the low level hardware during the past few years since the 100GE project started, especially when it comes to the ASIC and the FPGA technology [29]–[31]. Within memory technology, the classical RAM technologies considered at the beginning of the 100GE project [P1] (QDR SRAM, DDR3-DRAM, etc.) have also improved, but not to the same degree. However, new approaches to DRAM module design which are close to becoming commercially available gives cause for optimism within this field as well. Even with these advances in the underlying technology, from an architectural, algorithmic and digital design point of view, there are still plenty of challenges when moving to 100G and beyond.

#### 2.2. Ethernet as a carrier technology

Ethernet is a very popular and well-known technology, and it is estimated that the majority of all internet traffic either originates or terminates in an Ethernet device [P3]. With the introduction of 10G, 40G and 100G Ethernet interfaces, the standard definitely supports the speeds required to migrate further into the core networks. However, the Ethernet standard has traditionally been targeting enterprise or local area networks (LANs), and thus lacks many of the features required to be considered as a carrier grade technology. In order to address these shortcomings, the IEEE has developed a number of standards, enhancing the functionality of the original Ethernet standard. These include:

- 802.1Q: Virtual LAN [32]

- 802.1ad: Provider Bridging (PB) [33]

- 802.1ah: Provider Backbone Bridging (PBB) [34]

- 802.1Qay: PBB-Traffic Engineering (PBB-TE) [35]

- 802.3ah: Ethernet in the First Mile (with OAM) [36]

- 802.1ag: Connectivity Fault Management (OAM) [37]

- 802.1aq: Shortest Path Bridging [38]

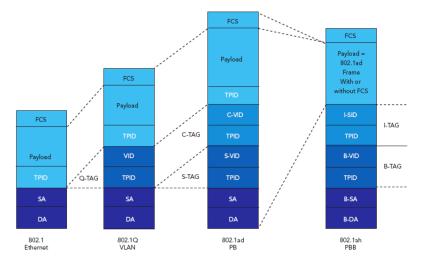

The evolution of the MAC frame format corresponding to these standards is depicted in Figure 2.3. The first issue to be solved is the fact that there is no logical separation of sub-networks within a standard Ethernet LAN. Hence, it is not possible to separate the traffic of different customers. This is also a potential security risk, as all LAN ports are part of the same broadcasting domain. With the introduction of VLANs, it became possible to separate a physical local area network (LAN) into multiple

Figure 2.3 – Evolution of the Ethernet header from standard 802.1 to Provider Backbone Briding [P3].

logical networks. However, the limited number of possible VLANs defined in the standard (4,096) was not enough to provide the desired level of separation within the networks. To improve the scalability, so called "Q-in-Q" or "Double Tagging" was introduced with Provider Bridging (PB) in 802.1ad, adding a second tag (S-TAG), which could be used to separate individual customers - leaving the C-TAG for further subdivision, e.g. within a customer's own network. Even so, the size of the S-TAG is still not sufficient for providers with more than 4,096 customers. To meet these and other challenges, the standard has been extended once again to support Provider Backbone Bridging (PBB). PBB takes a layered approach, encapsulating the entire PB frame, including the source and destination MAC addresses, in a larger PBB frame (earning it the nickname "MAC-in-MAC"). The outer PBB frame is only concerned with the transport through the backbone network, and thus uses the MAC addresses of the backbone endpoints (B-SA and B-DA) for forwarding. A B-TAG specifies a flooding domain (virtual networks) within the provider backbone. For logical separation of traffic from different customers, a much larger 24-bit I-SID tag is used, supporting up to 16 million different service instances (customers).

PBB-TE extends on this concept by discarding the flooding/broadcasting mechanisms, as well as the Spanning Tree Protocol (STP) altogether, targeting the protocol towards connection oriented network applications. The B-MAC addresses together with the B-TAG now specify a unique path though the network, using the B-TAG as a means of specifying alternate backup-paths. This adds a measure of resiliency, which is required for carrier class applications such as IPTV, by allowing protection switching in the network and also makes it possible to manually control the exact routing of the traffic. With the recent introduction of Shortest Path Bridging (SPB) to the VLAN standard in 2012, Ethernet now supports shortest path routing between bridge endpoints (e.g. two B-MACs) with multiple active paths. Hence, the backup paths can now be utilized for load sharing to increase performance in meshed networks.

The price for the extra functionality required to use Ethernet in carrier networks is more hardware and software complexity. New functions include flow based queuing and scheduling, advanced routing and forwarding, a more complicated protocol stack and advanced OAM functions, all of which increases the complexity of the network equipment compared to standard Ethernet, which is generally considered a simple and low cost technology. However, by adding more capabilities in terms of customer based Quality of Service differentiation, resiliency, scalability, customer isolation etc., these and other enhancements allow the Ethernet technology to reach into the core networks, instead of being restricted to the edges. There it can serve as a uniform carrier service (much like IP), which can run on native Ethernet links as well as other technologies such

as Passive Optical Networks (PONs), WiMAX, SDH/SONET or OTN. Furthermore, it retains its native capabilities such as multicast, easy connectivity (at the customer site), VLANs spanning multiple customer sites, and enables the network operator to increase overall link efficiency in the network by exploiting statistical multiplexing.

## 2.3. Standardization of 100 Gigabit Ethernet

The 40/100 Gigabit amendment to the Ethernet standard (802.3ba), begun in 2006, was released in its final version in June 2010 [9]. The following section describes some of the basics of the PCS layer and the CGMII interface in accordance with this standard.

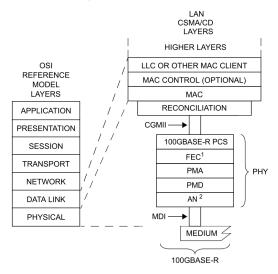

#### 2.3.1. 100G Media Independent Interface

Similar to the 10G standard, the 100G standard specifies a Media Independent Interface (MII) for interconnecting the PHY and the MAC. The new 100G MII (CGMII) interface, marked in Figure 2.4, is very similar to the 10G MII (XGMII) interface standard, using the same control sequences to indicate Error (/E), Start-Of-Frame (SOF), End-Of-Frame (EOF) and Idle characters. However, a number of simplifications have been made to the new interface compared to the 10G version. In contrast to the XGMII interface, which is 4 byte aligned, the new CGMII interface is 8 byte aligned, i.e. it uses 8 byte words. This affects functions such as SOF detection, since this character can only appear in the 1st byte position of the 8 byte word. Similarly, Idle sequences after the word containing the EOF character can only be a multiple of 8 bytes. Another restriction is placed on the occurrence of Error characters within the payload. Where XGMII allowed for single error characters everywhere in the binary data, the CGMII interface does not support single error characters in between the data bytes in the frame payload. Hence, if an error is detected in an 8 byte data word, the standard dictates that the

Figure 2.4 - Ethernet Layers (modified from [9]).

entire word should be decoded as error characters. This is due to the 64b/66b encoding format, which unlike the 8b/10b encoding used in XGMII does not allow the decoder to detect single byte or character errors in the payload.

#### 2.3.2. 100G Attachment Unit Interface

As was the case for the XGMII interface, the pin count of the CGMII interface makes it an unviable solution for chip-to-chip or board-to-board communications. Hence, when communicating between devices, such as the MAC and the physical transceiver, a more serialized Attachment Unit Interface (AUI) is used. For the 10G AUI (XAUI), this interface was comprised of four individual physical lanes, each running at 3.125Gbps using 8b/10b encoding. The 100G AUI (CAUI) builds on the same concept, but utilizes 64b/66b rather than 8b/10b encoding to reduce the coding overhead. The CAUI also introduces the concept of *virtual lanes*. Instead of splitting the traffic onto 4 physical lanes, the CAUI distributes the 66b blocks direction between 20 virtual lanes. Splitting the traffic onto 20 lanes makes it possible to adapt the output to several physical buswidth/line-speed combinations by simple multiplexing, such as 1x100G, 4x25G or 10x10G, depending on the physical output device.

In order to keep the different lanes correctly aligned, the XAUI uses a special 8b/10b encoded character, which is sent periodically over all lanes simultaneously. The receiving XAUI uses these alignment characters to verify, that all lanes are properly aligned and to correct the problem, should a misalignment occur. CAUI uses a similar approach, but has extended the alignment markers to fill up an entire 66b codeword on each virtual lane. Aside from a known three byte sequence, which is unique to each individual lane, the alignment markers also include a BIP8 even parity check sum calculated over all the 66b words from and including the last alignment marker. The last four bytes in the alignment marker is simply the inverse of the first four bytes, thus ensuring proper DC balance.

A final difference is the fact that the CAUI uses a scrambler in order to guarantee DC balance and transition density over the 66b words. The first two bits, which determine if the word is a control word or a data word, are kept unscrambled as they are used for 66b word alignment. The alignment markers are likewise kept unscrambled.

## 2.4. Framed Bit Error Rate Testing for 100GE

As the demand for 40 and 100 Gigabit systems rises, so does the demand for test equipment, which can keep up with this increase in line speed. As with all networking equipment, it is crucial to be able to measure the performance of 100GE systems, during development, deployment and use. A common metric of this performance is the so-called bit-error-rate (BER), i.e. the average ratio between the number of incorrectly received bits and the total transmitted bits count. At the beginning of this Ph. D., BER test equipment for Ethernet systems was only commercially available for speeds up to 40Gb/s [39], [40]. Simply extending these systems to run at 100Gb/s by increasing the clock speed proportionally was not a viable option. This would require extremely fast and expensive hardware and significantly increase the power consumption of such systems. A more viable approach to achieve the required throughput was by means of parallelization, i.e. increasing the number of processed bytes per clock cycle. While this increases the total chip area, parallelization allows for layer 1 bit error rate testing at 100Gbps without pushing the clock speed of such systems beyond reasonable levels.

Another important issue is the fact that the 100GE standard is designed to run over several physical transceivers or SerDes units. The first generations of 100 GE equipment transmit the traffic over several aggregated physical chip interfaces, e.g. 10x10G or 4x25G over a 100 Gigabit Attachment Unit Interface (CAUI) [9]. One approach for BER testing is to simply test the aggregated physical links individually. The 40GE/100GE standard lists this as an optional feature of 40GE/100GE devices and specifies the test parameters that should be used. However, this will not verify the various aggregation mechanisms, such as lane alignment, in the PCS and PMA Ethernet sub-layers, which are handled by the block implementing the CAUI. Nor will it allow the test data to pass through a Device Under Test (DUT) for verification. In order to fully verify the system, on both the tester and the DUT, the bit-error-rate tester (BERT) must be able to verify the aggregated stream as opposed to merely its sub components. Therefore, it must be attached at the 100 Gigabit Media Independent Interface (CGMII), the intra-chip interface between the MAC and the CAUI block (see Section 2.3, Figure 2.4). This poses the additional challenge of framing and deframing the BERT data at line speed to comply with the CGMII standard.

The following sections outline an FPGA implementation of a BERT system, which interfaces to a CGMII. The FPGA technology was chosen over an ASIC implementation due to the lower start up cost, as well their non-static nature, which rendered FPGAs highly suitable for the 100GE

field in 2009, where standards were still being finalized. Furthermore, the FPGA platform made it possible to extend the 100GE tester to work on the higher layers (MAC/IP) with limited modifications to the platform. Hence, it was possible to use the 100GE BERT as a stepping-stone towards a more advanced test system based on the final 40GE/100GE standard and continue to mature the product according to evolutions in customer needs. Implementing a 100GE CGMII BERT poses two main design challenges: Firstly, the test data must be validated and generated at the required line speed while keeping the resource utilization down in terms of power demands and logic consumption; and secondly, the test data must be inserted into an Ethernet framing structure at line speed for transport over the CAUI. The following subsections address these challenges, and presents and evaluates the power and logic cost of the FPGA based BERT implementation.

#### 2.4.1. Clock Frequency Versus Buswidth

Before moving on with the actual system design, it is first necessary to consider the trade-off between bus width and internal clock frequency. Since the required serial throughput of the design is very high compared to the achievable internal clock speed in modern FPGAs, it is necessary to introduce a high degree of parallelization. As mentioned in Section 2.1.2, one could simply replicate a slower circuit (e.g. 10Gbps) several times over and multiplex these streams together to form the required 100Gbps of throughput. Unfortunately, this way of parallelizing the system comes with a substantial overhead in terms of buffering, multiplexing, demultiplexing and controlling several aggregated streams, which makes this a far from optimal solution. Instead, this design reaches the required throughput using a single entity with a very wide bus in order to reduce the clock rate to a realistic level. The exact width of the system bus is a compromise between design complexity and clock speed. A larger bus width will decrease the required internal clock frequency of the FPGA, but increases the required FPGA resources and vice versa. Furthermore, the extreme cases of either a very high clock frequency or a very large data bus, heavily complicates the system design, which increases the development cost. In this project, a width/frequency combination of 512bits/195.31MHz has been selected. This lowers the required clock speed to one that can be realistically achieved in current FPGA technology, while keeping design complexity to a minimum. The reason for selecting exactly 512 or 29 bits is that bus widths which are a power of 2 are generally easier to work with in digital designs.

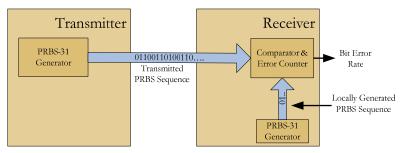

#### 2.4.2. Bit Error Rate Testing

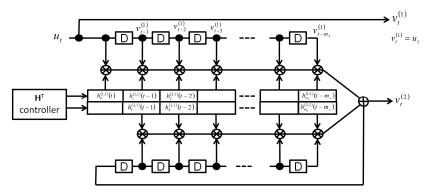

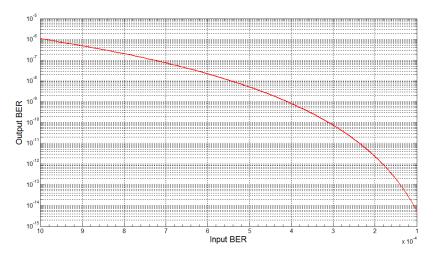

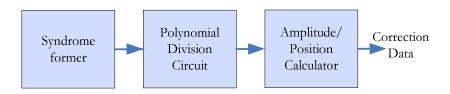

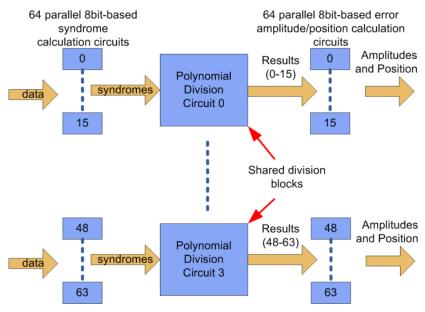

The heart of the 100G Bit Error Rate Tester (BERT) is the test pattern generation-and validation mechanisms, which are located on the transmit (TX) side and the receive (RX) side respectively (see Figure 2.5). The test traffic is generated in the transmitter using a Pseudo Random Bit Sequence (PRBS) generator. This component is able to generate a deterministic signal with properties similar to those of a random signal. Since the sequence is pseudo random, the resulting bit stream can be compared to a locally generated sequence at the receiver after transmission. Because the PRBS generator is implemented as a Fibonacci shift register [41], the receiver simply uses the first part of the received bit stream to instantiate its own local generator. Given that these first bits are received correctly, the receiver's PRBS generator is now synchronized with the transmitter, and any bits of the received sequence that deviate from the local sequence are counted as transmission errors. The sequence used in this implementation is the PRBS-31, which is recommended for link verification by the Ethernet 802.3ba standard[9].

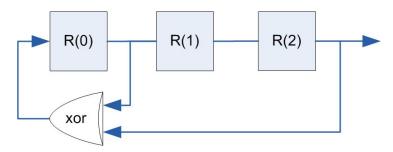

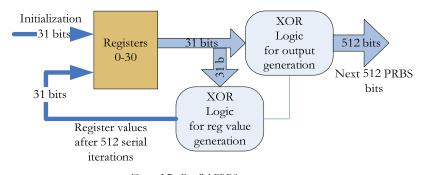

Generating a PRBS at 100 Gb/s is a non-trivial task. Using a serial implementation, as depicted in Figure 2.6, which produces only one bit per clock cycle by means of a Linear Feedback Shift Register (LFSR), would require an internal clock frequency of 100GHz, which is not feasible in current FPGAs. A well-known approach for implementing very high speed PRBS generators is to utilize multiple serial PRBS generators in parallel. These are initialized in such a way that the resulting multiplexed output corresponds to the serial sequence [41]. In investigating this approach, a serial generator for a PRBS-31 has been synthesized to run at a clock speed of 908 MHz in the fastest Altera FPGA on the marked in 2010 (EP4S100G2FA0I1) [40], [42]. Even at this very high frequency, a minimum of 111 PRBS generators must be running in parallel to produce 100 Gb/s. The resulting resource usage for the PRBS generators alone, without any multiplexing, retiming and control logic, is listed in Table 2.3 for a design using 128 serial generators running at 781.25MHz. In order to avoid the large resource consumption and high clock speed of such a

Figure 2.5 - Bit Error Rate Tester (BERT).

Figure 2.6 - Serial Fibonacci PRBS generator for the polynomial  $1 + x + x^3$ .

system, the parallel PRBS circuit design depicted in Figure 2.7 has been selected instead. This system is based on a serial Fibonacci LFSR [41], but parallelized to generate 512 bits of the PRBS sequence in a single clock cycle. This reduces the clock speed requirement to 195.3125MHz, which is both resource and power efficient and can be relatively easily obtained in commercially available FPGAs, while keeping the system complexity to minimum. The circuit consists of three parts: A 31-bit register, which holds the current state of the PRBS generator, and two combinatorial circuits for calculating the next 512 output bits and the next state of the register based on the current register state. The combinatorial circuits have been designed by pre-calculating the exclusive-OR (XOR) relationships between the current register values and the next 512 outputs of the serial LFSR implementation as well as the next state of the registers corresponding to 512 serial shifts. The calculation of each output bit and each new register value can then be performed in parallel. The resulting parallel generator circuit is able to produce the desired PRBS-31 sequence [9] at 100 Gb/s while keeping both the resource and the power consumption to a minimum.

As seen in Table 2.3, the number of combinational lookup tables (LUTs) and especially the number of registers is dramatically decreased compared

Figure 2.7 - Parallel PRBS generator.

|                                | Serial PRBS<br>generator array (a) | Parallel PRBS<br>generator (b) | Available in the FPGA (c) [42] |

|--------------------------------|------------------------------------|--------------------------------|--------------------------------|

| Combinational<br>Adaptive LUTs | 11.904 (93*128)                    | 564                            | 182.400                        |

| Registers                      | 3.968(31*128)                      | 31                             | 182.400                        |

| Required clock frequency       | 781.25 MHz                         | 195.3125<br>MHz                | N/A                            |

| Maximum clock frequency        | 808 MHz                            | 597 MHz                        | N/A                            |

Table 2.3 - PRBS Generator Synthesis Results

to the approach using serial PRBS generators. The mathematical algorithm used to generate the parallel PRBS generator is described below.

#### 2.4.2.1. Calculating the parallel XOR equations

The parallel equations for the 512bit wide PRBS generator have been auto generated in VHDL syntax using a Matlab program based on the approach described in [43]. The following example uses the simple LFSR depicted in Figure 2.6 with the polynomial  $x^3+x+1$  to illustrate how these equations can be mathematically derived by means of matrix multiplication. Based on the PRBS polynomial, it is possible to set up a transition matrix (T) describing the next state of the registers (i.e. the state after 1 clock cycle) based on their current state:

$$\begin{bmatrix} 1 & 0 & 1 \\ 1 & 0 & 0 \\ 0 & 1 & 0 \end{bmatrix} \begin{vmatrix} R(0) = R(0)xorR(2) \\ R(1) = R(0) \\ R(2) = R(1) \end{vmatrix}$$

Figure 2.8 - Transition Matrix: T1.

By multiplying this matrix with itself modulo 2 (T2 mod 2), the equations for the register state after two clock available cycles are obtained:

$$\left[\begin{array}{ccc} 1 & 1 & 1 \\ 1 & 0 & 1 \\ 1 & 0 & 0 \end{array}\right] \left|\begin{array}{ccc} R(0) = R(0)xorR(1)xorR(2) \\ R(1) = R(0)xorR(2) \\ R(2) = R(0) \end{array}\right.$$

Figure 2.9 - Transition Matrix: T2

Generalizing this approach, it is possible to obtain the equations for the register values after an arbitrary number of clock cycles (q), corresponding

to q register shifts. By implementing these equations directly in hardware, the register states can thus be advanced corresponding to 512 serial shifts in a single clock cycle. Since the output of the PRBS generator is always the value of the last register in the LFSR, in this case R(2), the parallel equations corresponding to the next 512 bits in the sequence can be obtained by simply running through all the transition matrixes  $\mathbf{T}_q$  from q=1 to q=511 and extracting the 512 equations of the last register. In the example above, the equations for the first output bits would read: Output(0)=R(2), Output(1)=R(1), Output(2)=R(0), Output(3)=R(0) xor R(2), etc. Using the same algorithm, the PRBS-31 polynomial  $x^{31} + x^{28} + 1$  is converted into parallel equations for direct implementation in hardware.

#### 2.4.3. Framed BERT

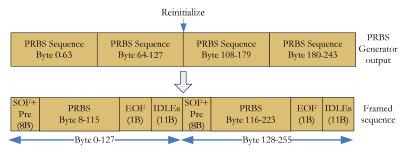

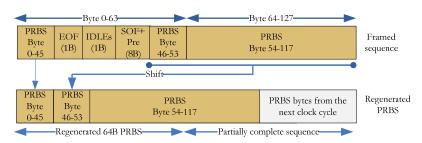

Since CGMII requires the data to be in an Ethernet frame format, the necessary preamble and inter frame gap (IFG) must be inserted at regular intervals, as depicted in Figure 2.10, to provide framing during transit. At the receiver, the same overhead must be removed to reproduce the original PRBS sequence (Figure 2.11). In order to get a bus width of 512 bits, the native 64bit bus of the CGMII interface is extended eight times, i.e. eight 64bit CGMII words are transmitted over the interface in each clock cycle. The following section will describe the basic operation of the 100Gbit framer/deframer, which communicates with the Ethernet PHY via this interface.

The generated frames consist of a static Start-of-Frame (SOF) and Preamble sequence, a payload field, an End-of-Frame (EOF) character and an idle sequence of variable length. Hence, the PRBS sequence must be broken up into sub-sequences which fit into the payload part of the frames. After transmission, the fragmented sequences must be reassembled at the other end to reproduce the original stream. The challenging factor is that these functions must be performed on 512 bits (64B) in parallel to reach 100Gb/s.

On the transmission (TX) side of the framed BERT, the framing is performed as depicted in Figure 2.10. In each clock cycle, a 64B vector is delivered from the PRBS generator. The overhead bytes between each frame payload (SOF, idle bytes, etc) are inserted by simply overwriting the generated PRBS bytes in the appropriate positions. The lost PRBS bytes are regained by reinitializing the PRBS generator with the first 31 bits of the overwritten sequence, which will cause the generator to repeat the overwritten bytes as the first part of the next payload. This behavior is inherent to the Fibonacci type LFSR [41], on which the parallel system is based, where the initial register state is always the first 31 bits to exit the generator.

Figure 2.10 - Framing of two adjacent minimum size frames.

Figure 2.11 - Regenerating the original pseudo random bit sequence.

Framing on the transmission side is simplified by always inserting the overhead bytes in the same positions. On the receiver side of the BERT, one cannot exercise the same control over the exact positioning of the control bytes on the 64B bus. The sequence may be shifted during transmission, and the idle period may be lengthened or shortened to compensate for deviations between the receivers' and the transmitters' local clock signals. As a result, more complex cases exist, like the one depicted in Figure 2.11, where a 64B vector contains PRBS data from two adjacent frames. In order to regenerate the original PRBS sequence, the frames are passed through a system, which deletes the overhead bytes and shifts the fragmented PRBS data together to close the resulting gap. The system takes advantage of the fact that only one sequence of overhead bytes can exist in a 64B vector due to the minimum size of Ethernet frames. This assumption reduces the extraction to a simple shift operation followed by a 2-to-1 multiplexing, a process which can be easily pipelined for higher clock speeds. The resulting PRBS stream is then fed to the bit error rate counter as if it was a serial unframed bit stream.

#### 2.4.4. Synthesis Results

The described system has been synthesized to an Altera Stratix IV GT FPGA (EP4S40G2F40I2) [42]. The entire BERT circuit implementing both the transmitter and the receiver takes up 12,077 Combinational

Adaptive Look-Up Tables (CALUTs) and 10,572 registers with a maximum frequency of 257 MHz. This accounts for the two parallel PRBS generators, the CGMII framing/deframing circuitry and the overall control and glue logic. As anticipated, the deframing function is by far the most critical component in terms of critical path delay and logic utilization. Even so, the proposed design offers a very compact solution, which can be easily pipelined to support even greater throughput or implementation in more modest FPGAs. The system has been successfully and repeatedly verified as part of the first generation Xena 100GE tester, and used to debug other parts of the 100GE system as well as to verify interoperability between the Xena and the TPACK 100GE implementations.

#### 2.4.5. Conclusion on Framed BERT

This section has presented an overview of a novel design for a Bit-Error-Rate-Tester, which is compatible with 100 Gigabit Carrier Ethernet over a 100 Gigabit Media Independent Interface (CGMII). By means of parallelization of the PRBS and framing functions, the BERT has been efficiently synthesized to current FPGA technology with minimal resource and energy requirements. Running bit-error-rate tests over a CGMII interface provides an effective tool for testing both internal PCS/PMA functions as well as providing quality measurements of the logical 100 Gigabit Ethernet links of future transport networks.

#### 2.5. Chapter Summary

This chapter has given an overall introduction to the new 100 gigabit Ethernet standard as well as the challenges of implementing Ethernet equipment with this high line rate. As an example of an actual 100 gigabit Ethernet implementation, the 100G framed BERT is presented, which was a key component in the first proof of concept in the 100GE project. The important subjects of address lookup and scheduling, which have only been mentioned briefly in this chapter, will be elaborated further in chapters 3 and 4.

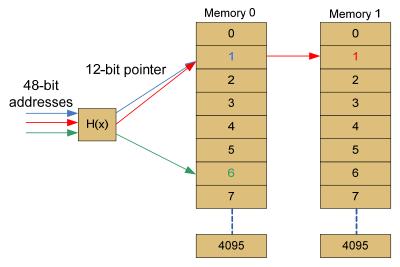

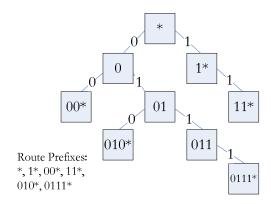

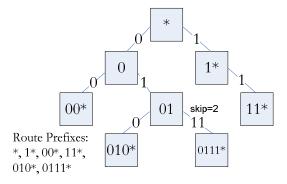

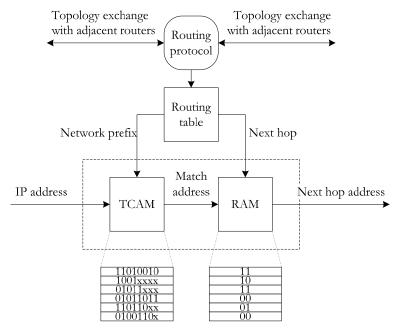

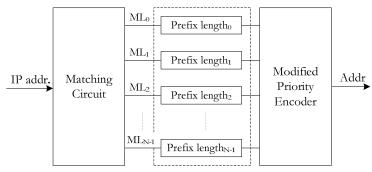

### 3. Address Lookup

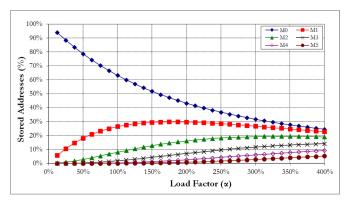

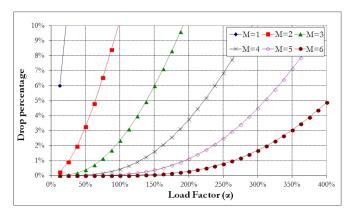

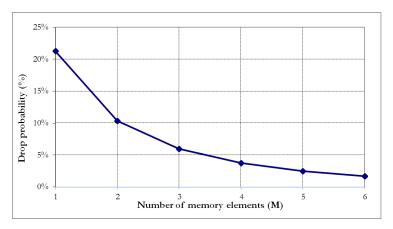

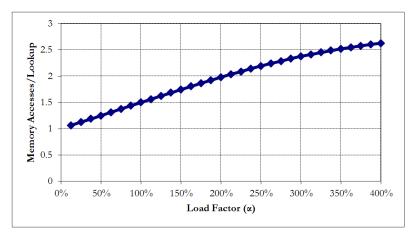

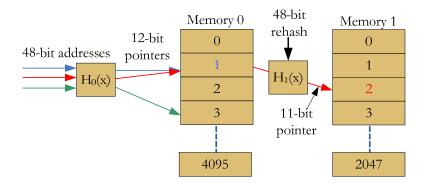

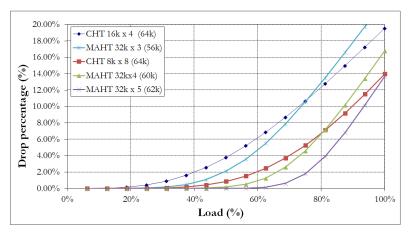

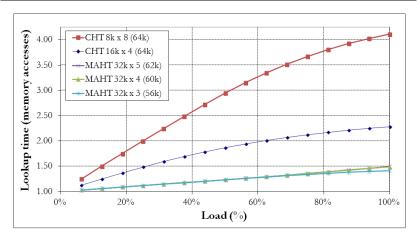

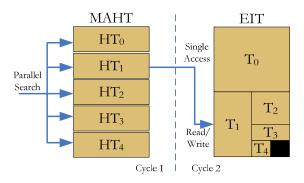

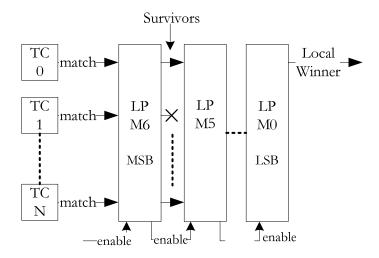

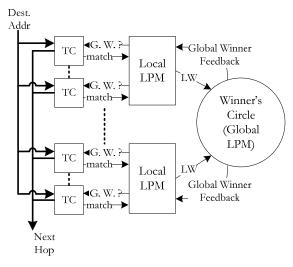

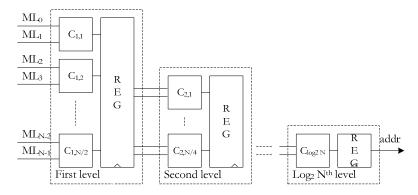

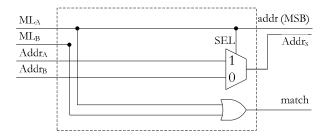

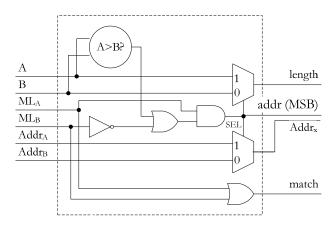

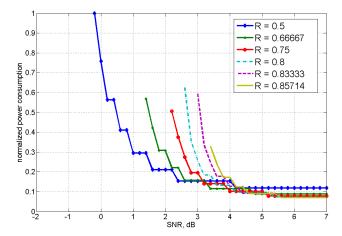

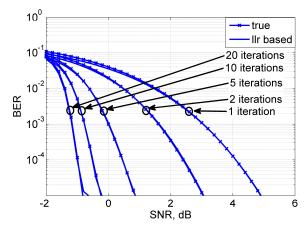

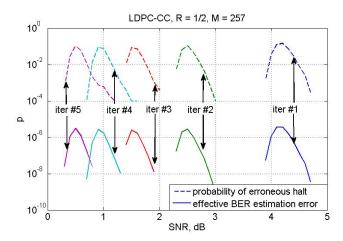

As mentioned in Section 2.1.3, the ability to find a data entry based on the address information of a datagram is a key feature of most network nodes. These data entries may contain forwarding information, QoS level, statistics etc. This chapter is mainly focused on finding the forwarding information from an address, but the techniques are transferable to the other data structures as well.